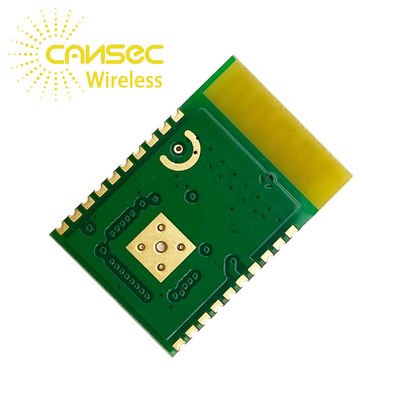

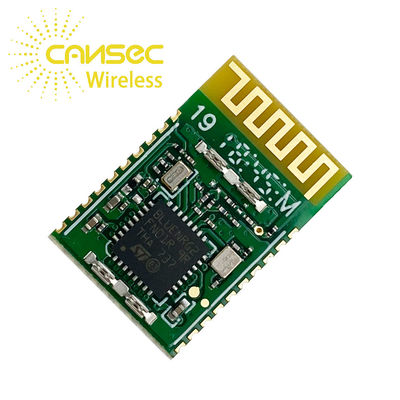

Módulo inalámbrico inalámbrico de baja potencia del St Bluenrg-2 del bajo costo Ble232SA-A del módulo de Bluetooth

|

|

|

|

|

|

|

|

|

|

|

|

Temperatura de la operación

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Módulo inalámbrico inalámbrico barato del St Bluenrg-2 del módulo de baja potencia Ble232SA-A de Bluetooth

Descripción

El módulo de la serie de BLE232SA/UA se diseña basado en el BlueNRG-2 de la compañía del ST. El BlueNRG-2 es un sistema-en-microprocesador unimodal bajo de la energía de Bluetooth de la misma energía baja (BLE5.0) obediente con la especificación de Bluetooth.

El BlueNRG-2 extiende las características del procesador de red premiado de BlueNRG, permitiendo el uso de la corteza integrada M0 para el código de aplicación de funcionamiento del usuario.

El BlueNRG-2 incluye 256kB de memoria Flash programada, de 24 kB de la memoria ram de estático con la retención (dos bancos 12kB) y de SPI, UART, periférico estándar del interfaz de comunicaciones de I2C. También ofrece contadores de tiempo, el perro guardián, el controlador multifuncionales del RTC y dma.

Un ADC está disponible para interconectar con los sensores análogos, y para leer la medida del monitor integrado de la batería. Un filtro digital está disponible para procesar la corriente de PDM.

El BlueNRG-2 ofrece el mismo funcionamiento excelente del RF como la radio de BlueNRG, y el convertidor de gran eficacia integrado de DC/DC guarda las mismas características ultrabajas del poder, pero el BlueNRG-2 mejora el consumo actual del modo de sueño de BlueNRG permitiendo un aumento posterior en el curso de la vida de la batería de los usos.

Usos

- Relojes

- Aptitud, salud y deportes

- Consumidor médico

- Seguridad/proximidad

- Teledirigido

- Automatización casera e industrial

- Vida ayudada

- Periférico del teléfono móvil

- Iluminación del peripher de la PC

Características

- Sistema-en-microprocesador del solo modo de la energía baja de Bluetooth obediente con Bluetooth 5,0 especificaciones:

papeles simultáneos del amo, auxiliares y múltiples

Extensión de la longitud del paquete de datos del LE

- Voltaje de fuente de funcionamiento: de 1,7 a 3,6 V

- Regulador linear integrado y convertidor descender de DC-DC

- Gama de temperaturas de funcionamiento:

-30 °C al °C 85

- De alto rendimiento, base basada de 32 bits de la arquitectura de la corteza M0 del ultra-bajo-poder

- Flash programable de 256 kB

- 24 kB RAM con la retención (dos 12 bancos del kB)

- 1 interfaz de x UART

- 1 interfaz de x SPI

- 2 x I interfaz del ² C

- 15GPIOs

- contador de tiempo multifuncional de 2 x

- 10-bit ADC

- Perro guardián y RTC

- Controlador dma

- Procesador de la corriente de PDM

- Oscilador cristalino de 32 megaciclos

- oscilador cristalino de 32 kilociclos

- Monitor de voltaje de la batería y sensor de temperatura

(en el conector de antena)

- Presupuesto excelente del vínculo del RF (DB hasta 96)

- RSSI exacto para permitir control de poder

8,3 mA TX de actual (@ -2 dBm, 3,0 V)

- Abajo a 1 consumo actual del µA con la pila activa de BLE (modo de sueño)

- Consumo actual medio del anuncio

µA 15,34 (ms 1000), 1 año del intervalo del anuncio, 8 meses, 19 días con la batería de 230 mAh (CR2032)

- Consumo actual medio de la conexión

µA 7,059 (ms 1000), 3 años del intervalo de la conexión, 10 meses, 12 días con 230mAhbattery (CR2032)

- Conveniente para los usos constructivos obedientes con las regulaciones siguientes de la radiofrecuencia: EN 300 328, EN 300 440, parte 15, ARIB STD-T66 de la ETSI de la FCC CFR47

- Cargador de arranque preprogramado vía UART

- Hasta +8 de potencia de salida disponibles del dBm

Nota A: las características del ll de BLE5.0 no se apoyan actualmente, sino que es la mayoría del microprocesador del coste-funcionamiento en apoyo de BLE5.0.

¡Su mensaje debe tener entre 20 y 3.000 caracteres!

¡Su mensaje debe tener entre 20 y 3.000 caracteres! ¡Por favor revise su correo electrónico!

¡Por favor revise su correo electrónico!  ¡Su mensaje debe tener entre 20 y 3.000 caracteres!

¡Su mensaje debe tener entre 20 y 3.000 caracteres! ¡Por favor revise su correo electrónico!

¡Por favor revise su correo electrónico!